1.摩尔定律指引过去几十年集成电路产业发展。

摩尔定律由英特尔创始人之一的戈登·摩尔提出,其核心内容为:在价格不变时,集成电路上可以容纳的晶体管数量每 18-24 个月便会增加一倍,即:处理器性能大约每两年翻一倍,同时价格下降为之前的一半。在过去几十年,摩尔定律指引着集成电路产业发展。随着工艺进步,集成电路上晶体管密度不断提升,驱动计算机性能保持几何级数增长,而性能的快速提升则推动芯片价格迅速下降。

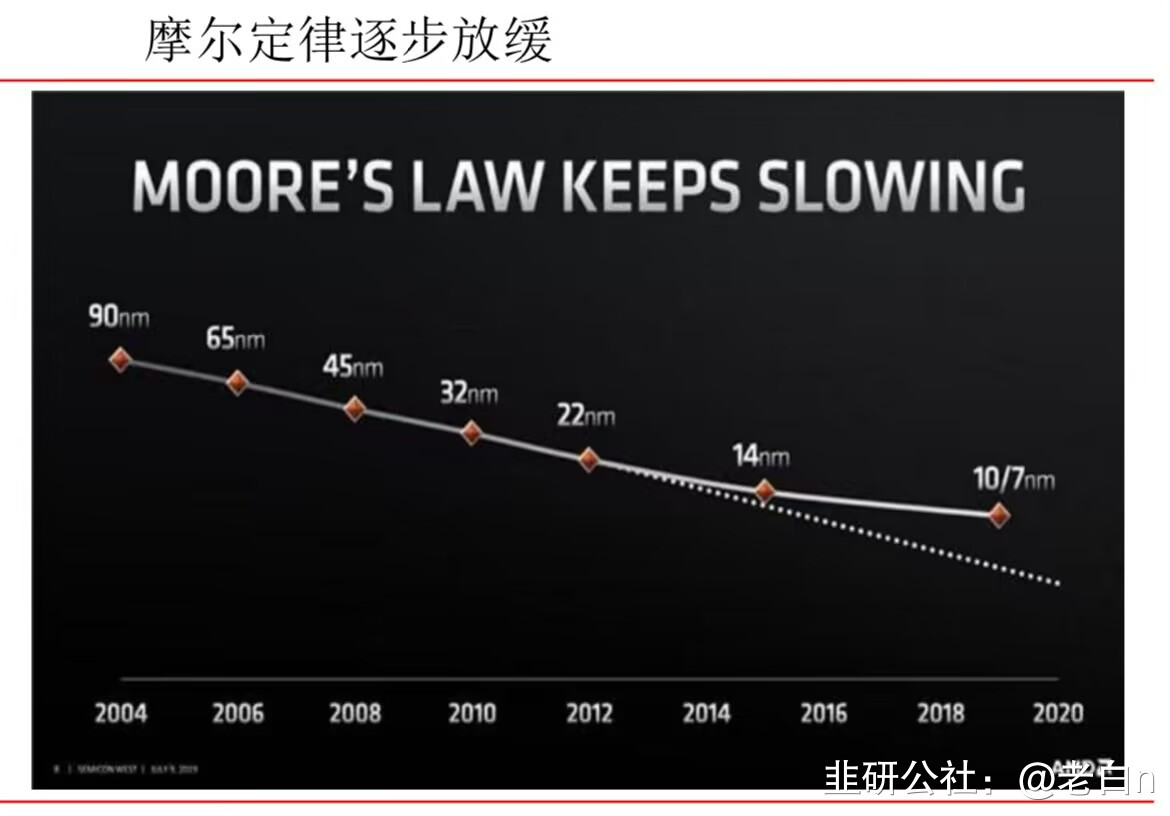

“摩尔定律”发展陷入瓶颈,集成电路进入后摩尔时代。从1987年的1um 制程至2015年的14nm制程,集成电路制程迭代大致符合“摩尔定律”的规律。但自 2015年以来,集成电路先进制程的发展开始放缓,7nm、5nm、3nm 制程的量产进度均落后于预期。随着台积电宣布 2nm 制程工艺实现突破,集成电路制程工艺已接近物理尺寸的极限,摩尔定律发展陷入瓶颈,行业进入了“后摩尔时代”。

2.Chiplet 可在不改变制程的前提下提升算力,且保证芯片良率。Chiplet俗称“芯粒”,又称“小芯片组”,从字面意义上可以理解为“粒度更小的芯片”。它是将一类满足特定功能的die,通过die-to-die内部互联技术实现多个模块芯片与底层基础芯片封装在一起,进而形成一个系统芯片。它可以有效提升芯片的集成度,是在不改变制程的前提下提升算力,并且保证芯片生产良率的一种手段。

3.后摩尔时代,Chiplet成为提高芯片算力与集成度的重要途径。后摩尔时代,随着集成度提升,SoC开始在供电、功耗和散热等方面面临挑战,芯片全流程设计成本大幅增加,而制程工艺接近极限,每次迭代升级都需要付出极大的额外成本,而随着性能提升,发热功耗等方面的问题也日益凸显,继续追求极致工艺的意义已经不大。Chiplet 作为当下较受关注的半导体发展方向,可有效降低能够有效降低芯片设计与制造的门槛,提升良率和节约成本,因此成为摩尔定律趋缓背景下提升芯片集成度与算力的重要途径。

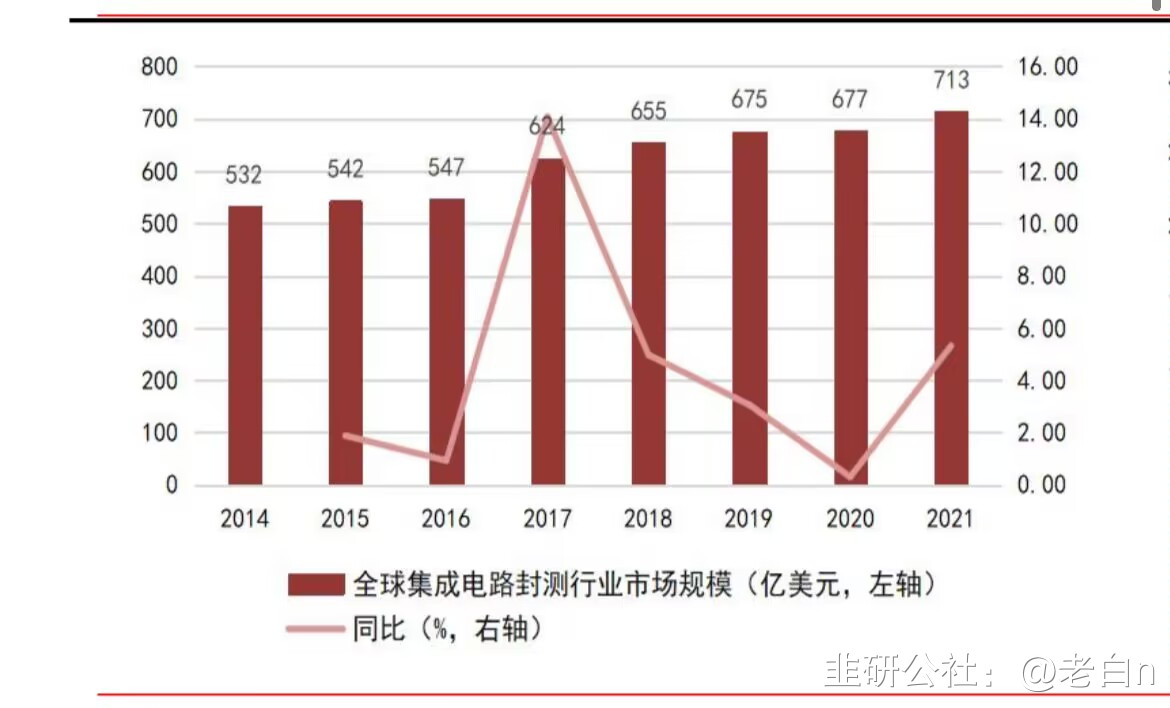

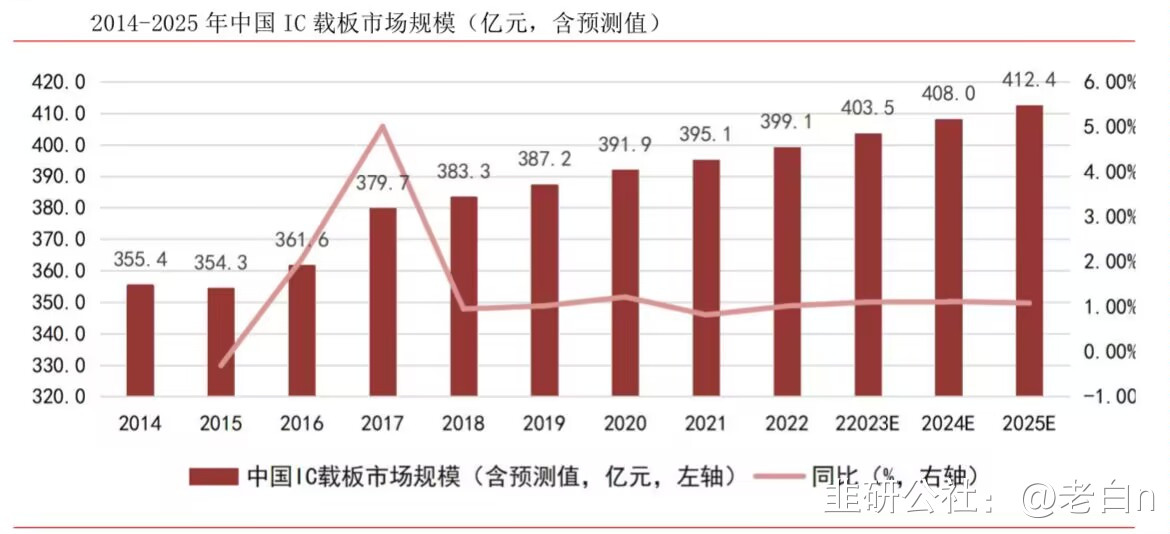

4.Chiplet技术持续推进,先进封装、IC载板、半导体IP等多环节受益。 先进封装与测试:Chiplet需要先进封装技术作为支持,此外,且在生产完成后需要进行全检,增大集成电路测试需求,利好在先进封测布局领先的封测厂商与测试设备供应商;IC载板:IC载板为先进封装的关键材料,国产替代率低,行业存在较大供需缺口,以兴森、深南为代表的内资PCB企业积极扩产,以满足下游客户需求;半导体IP:Chiplet开启IP复用新模式,即硅片级别的复用,不同功能的IP可灵活选用选择不同的工艺分别进行生产,从而可以灵活平衡计算性能与成本。随着Chiplet 技术演进,IP供应商的商业灵活性和发展空间得到拓展。相关企业已整理完毕,有需要可私聊。

- 1